Miks kasutada Xilinxi FPGA XC3S500E-4FTG256I?

Kui olete elektroonikainsener, võite tunda kiipi XC3S500E-4FTG256I .

Seda Field Programmable Gate Array (FPGA) kasutatakse laialdaselt erinevates rakendustes, alates olmeelektroonikast kuni tööstusliku juhtimise, lennunduse, sõjalise ja muude valdkondadeni.

FPGA on pooljuhtseade, mis koosneb programmeeritavate ühenduste kaudu ühendatud konfigureeritavate loogikaplokkide (CLB) maatriksist. Kasutaja määrab need ühendused SRAM-i programmeerimisega. CLB võib olla lihtne (JA, VÕI väravad jne) või keeruline (RAM-i plokk). FPGA võimaldab disainis muudatusi teha ka pärast seda, kui seade on PCB-sse joodetud.

Sellest artiklist saate teada mõningaid Xilinxi XC3S500E-4FTG256I põhitõdesid ning uurite ka selle professionaalset kasutusviisi ja selle funktsioone.

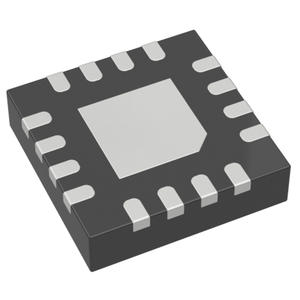

Mis on XC3S500E-4FTG256I?

XC3S500E-4FTG256I kuulub Spartan-3E FPGA seeriasse, mille on kujundanud Xilinx.

Spartan-3E perekond pakub kulutõhusat FPGA-lahendust väikese võimsuse tarbimise, suure jõudlusega ja täiustatud süsteemitaseme funktsioonidega.

Xilinx Zynq FPGA

XC3S500E-4FTG256I sisaldab 500 000 süsteemiväravat, 772 kasutaja sisendit/väljundit ja 36 plokk-RAM-i.

See töötab maksimaalsel sagedusel 400 MHz ja selle südamiku pingevahemik on 1,14 V kuni 1,26 V.

XC3S500E-4FTG256I kasutatakse tavaliselt sellistes rakendustes nagu lennundus ja kaitse, autotööstus, ringhääling, tarbija-, kõrgjõudlusega andmetöötlus, tööstuslik, meditsiiniline ja teaduslik, testimine ja mõõtmine.

Taotlege originaali ja uut Xilinxi XC3S500E-4FTG256I FGPA kohe

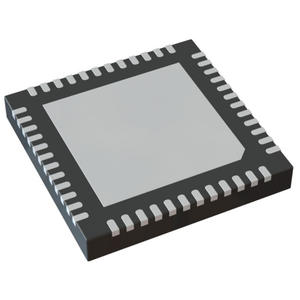

XC3S500E-4FTG256I omadused

• SelectIO signalisatsioon

– kuni 633 I/O kontakti

– kaheksateist ühe otsaga signaalistandardit

– kaheksa diferentsiaalsignaali standardit, sealhulgas LVDS ja RSDS

– Double Data Rate (DDR) tugi

• Loogikaressursid

– rohkelt loogikalahtreid koos nihkeregistri võimalusega

– laiad multiplekserid

– kiire ettevaatamise loogika

– spetsiaalne 18 x 18 kordaja

– JTAG-i loogika ühildub IEEE 1149.1/1532-ga

• Valige RAM-i hierarhiline mälu

– kuni 1728 kbit kogu ploki RAM-i

– kuni 432 kbit kogu hajutatud RAM-i

• Digitaalse kella haldur (neli DCM-i)

– Kella moonutuse kõrvaldamine

– sagedussüntees

– Kõrge eraldusvõimega faasinihe

English

English Español

Español Português

Português русский

русский français

français 日本語

日本語 Deutsch

Deutsch Tiếng Việt

Tiếng Việt Italiano

Italiano Nederlands

Nederlands ไทย

ไทย Polski

Polski 한국어

한국어 Svenska

Svenska magyar

magyar Malay

Malay বাংলা

বাংলা Dansk

Dansk Suomi

Suomi हिन्दी

हिन्दी Pilipino

Pilipino Türk

Türk Gaeilge

Gaeilge عربى

عربى Indonesia

Indonesia norsk

norsk čeština

čeština Ελληνικά

Ελληνικά Українська

Українська Javanese

Javanese فارسی

فارسی български

български ລາວ

ລາວ Latine

Latine Қазақ

Қазақ Euskal

Euskal Azərbaycan

Azərbaycan slovenský

slovenský Македонски

Македонски Lietuvos

Lietuvos Eesti Keel

Eesti Keel Română

Română Slovenski

Slovenski Српски

Српски 简体中文

简体中文 繁體中文

繁體中文 Беларус

Беларус